Coherent Receiver

Zeit-, Phasen- und Frequenzsynchronisation von

Kostengünstige DVB-T-USB-Empfänger

Software Defined Radios in a Multi-Channel

Coherent Receiver

Xuan Liu

Überzetzung durch: 19NL001

▪ Motivation und Zielsetzung

▪ Theoretischer Hintergrund

▪ Kohärentes Mehrkanal-Empfängermodell

▪ Hardware- und Software-Implementierung

▪ Überprüfung und Messung

▪ Fazit und Ausblick

Motivation

Software Defined Radio (SDR)

▪ Vorteile

• Weniger Bedarf an dedizierter Hardware

• Erfüllen Sie Mehrzweck mit einem Modul

▪ Nachteile

• Die meisten SDR-Plattformen sind ziemlich teuer

• Weniger Machbarkeit für mehrere Geräte

RTL-SDR (DVB-T Receiver) ist derzeit der günstigste (ca. 10 €) und

hat überraschend gute Leistung in Bezug auf die allgemeine Benutzerfreundlichkeit

Zielsetzung:

▪ Theoretische Untersuchung von RTL-SDR

▪ Aufbau eines kohärenten Vierkanalempfängers mit RTL-SDRs

• Zeitsynchronisation

• Frequenzsynchronisation

• Phasensynchronisation

▪ Messung und Überprüfung

Theoretischer Hintergrund:

▪ Motivation und Zielsetzung

▪ Theoretischer Hintergrund

▪ Kohärentes Mehrkanal-Empfängermodell

▪ Hardware- und Software-Implementierung

▪ Überprüfung und Messung

▪ Fazit und Ausblick

Theoretischer Hintergrund

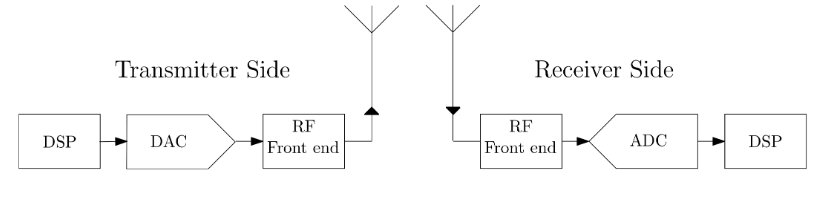

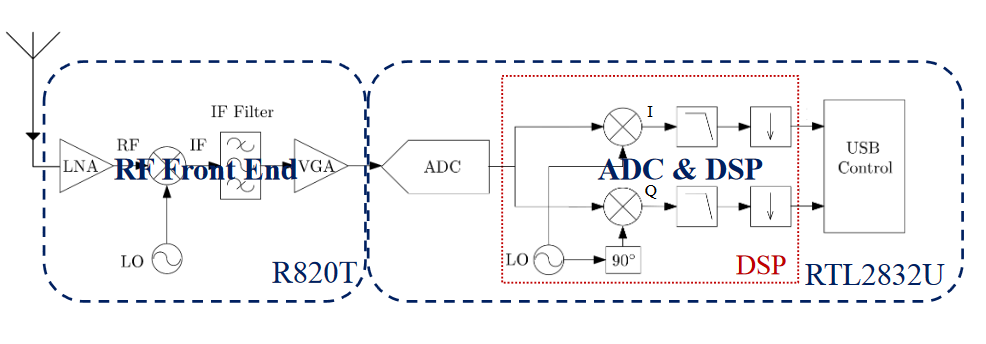

Software Defined Radio

▪ Software Defined Radio (SDR) bietet eine Lösung zum Aufbaueines flexiblen und

kosteneffizientes drahtloses Netzwerk durch Software, die einige oder alle der definiert Funkfunktionen.

▪ SDR-Blockdiagramm

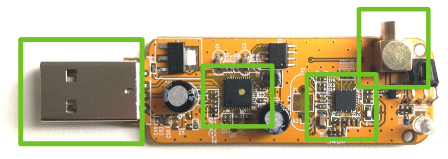

DVB-T-Dongle (RTL-SDR)

▪ MCX-Buchse

▪ USB 2.0

▪ Tuner-Chip R820T

▪ Demodulator-Chip RTL2832U

DVB-T als SDR

Kohärentes Mehrkanal-Empfängermodell

▪ Motivation und Zielsetzung

▪ Theoretischer Hintergrund

▪ Kohärentes Mehrkanal-Empfängermodell

▪ Hardware- und Software-Implementierung

▪ Überprüfung und Messung

▪ Fazit und Ausblick

Mehrkanaliges kohärentes Empfängermodell

▪ Kohärente Empfängeranforderung

• Der Abtasttakt muss zwischen den Empfängern synchronisiert werden

• Der Startzeitpunkt der Abtastung muss zwischen den Empfängern ausgerichtet sein

▪ Anwendungen, die einen phasensynchronen Empfang erfordern

• Frequenzsynchronisation

• Phase Vorkenntnisse

Mehrkanaliges kohärentes Empfängermodell

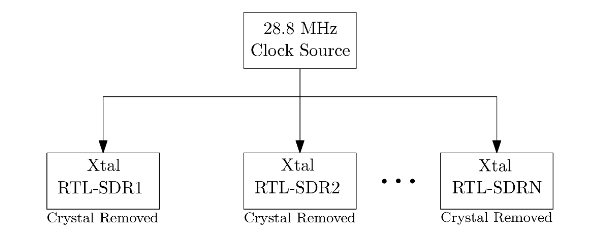

▪ Abtasttakt- und Frequenzsynchronisation

• Jitter und Drift der Uhr

• Der 28,8-MHz-Taktkristall ist die Einzeltaktquelle für RTL-SDR

• Lösung: Gemeinsame Nutzung einer gemeinsamen Taktquelle zwischen RTL-SDRs

Mehrkanaliges kohärentes Empfängermodell

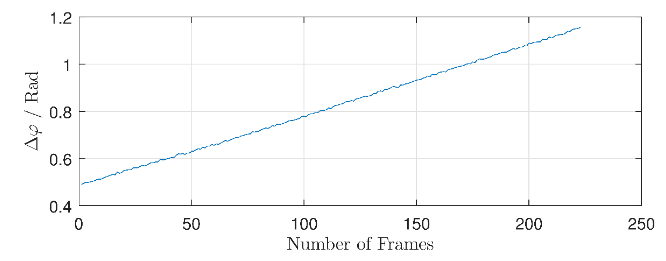

▪ Fractional- N PLL-Restfrequenzfehler

• Kontinuierliche Phasendrift zwischen zwei RTL-SDRs, auch bei gemeinsamer Nutzung

der Clock entsteht eine Frequenzinkongruenz

• Verborges 17.th Bit des fractional- N PLL wird zufällig bei RETUNE eingestellt

• Frequenzfehlanpassung nimmt diskrete Werte an

Mehrkanaliges kohärentes Empfängermodell

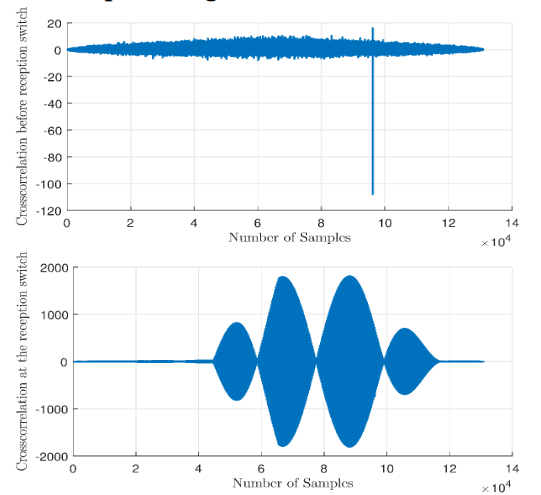

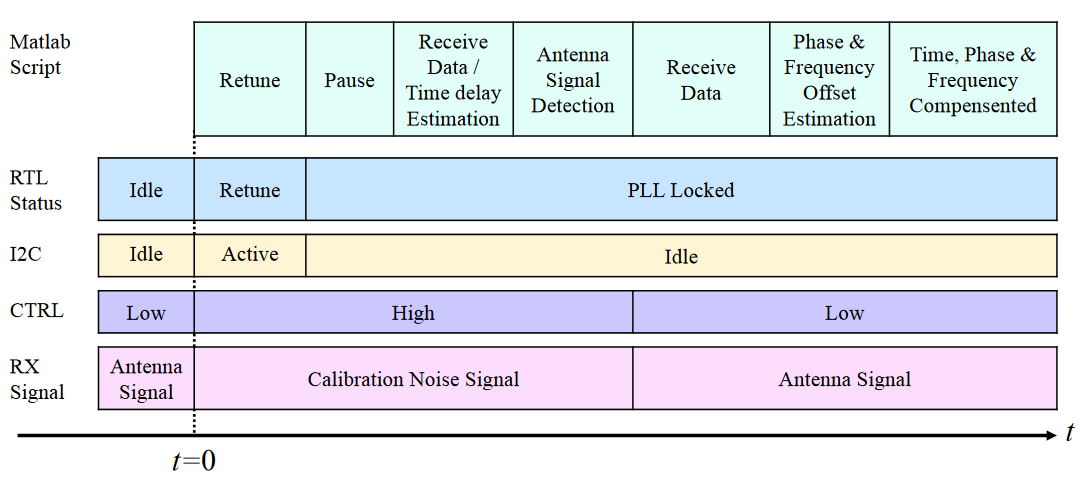

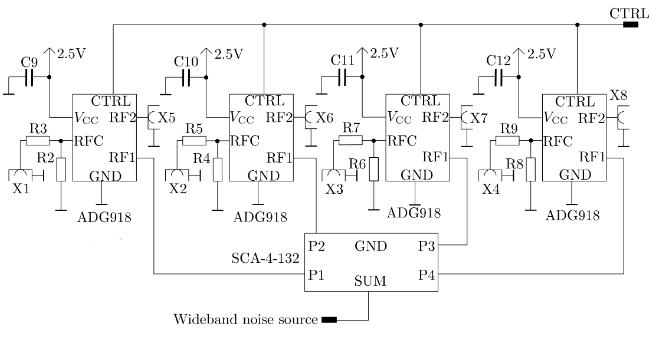

▪ Zeitsynchronisation

• USB-Kommunikation einige Millisekunden

• PLL-Sperrzeit

max. 5ms

• Lösung: In jedes RTL-SDR am wird ein Breitband-Rauschsignal eingespeist

Beginn des Empfangs und Kreuzkorrelation wird berechnet

➢ Die Autokorrelation von weißem Rauschen ist eine Dirac-Delta-Funktion

➢ Zu Beginn des Antennenempfangs ist keine erneute Abstimmung erforderlich

• Der Zeitversatz bleibt konstant, solange keine Samples verloren gehen

Mehrkanaliges kohärentes Empfängermodell

▪ Phasensynchronisation

• Zufälliger Phasenversatz aufgrund der gebrochenen N- PLL im Tuner-Chip

R820T tritt bei jeder Neuabstimmung auf

• Lösung: Winkeldifferenz zwischen zeitlich ausgerichtetem Rauschsignal von RTL-

SDRs ist der Phasenversatz

• Der Phasenversatz bleibt konstant, solange keine Neuabstimmung erfolgt

Hardware- und Software-Implementierung

▪ Motivation und Zielsetzung

▪ Theoretischer Hintergrund

▪ Kohärentes Mehrkanal-Empfängermodell

▪ Hardware- und Software-Implementierung

▪ Überprüfung und Messung

▪ Fazit und Ausblick

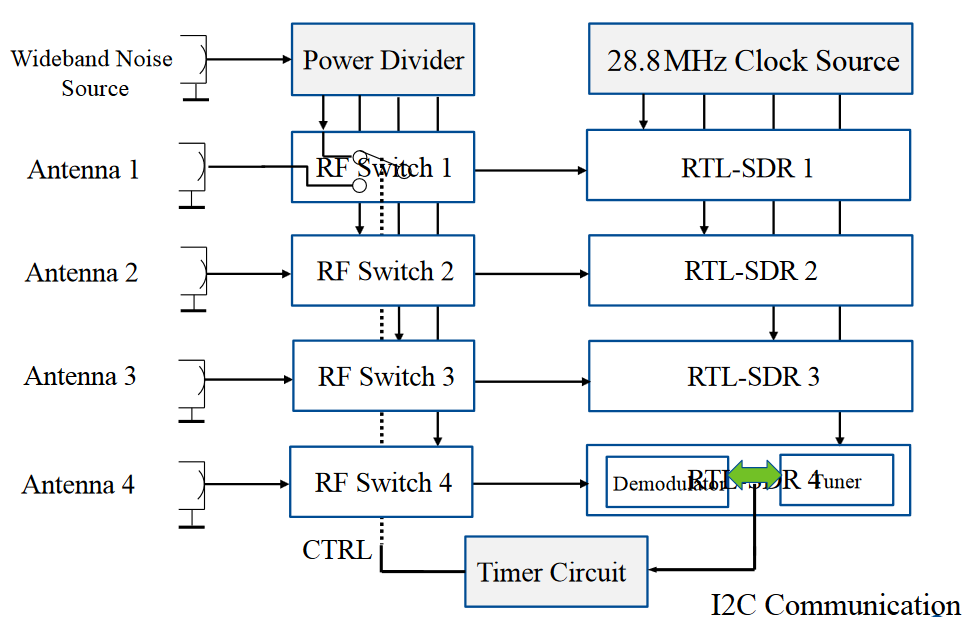

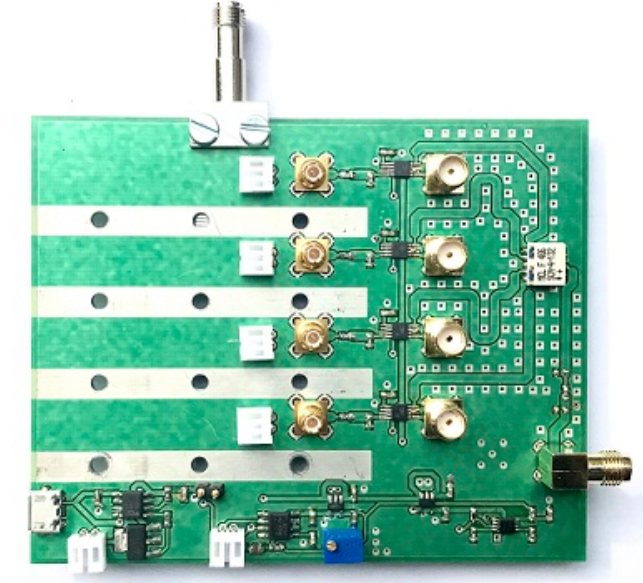

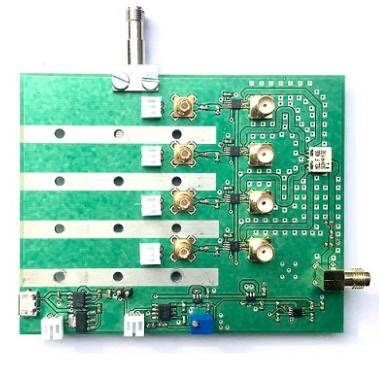

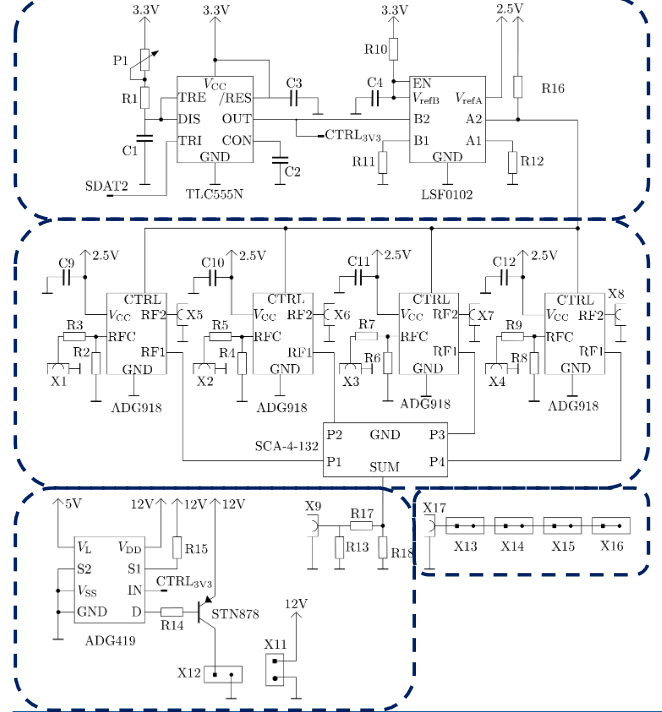

Hardware- und Software-Implementierung

Hardware- und Software-Implementierung

Hardware- und Software-Implementierung

Überprüfung und Messung

▪ Motivation und Zielsetzung

▪ Theoretischer Hintergrund

▪ Kohärentes Mehrkanal-Empfängermodell

▪ Hardware- und Software-Implementierung

▪ Überprüfung und Messung

▪ Fazit und Ausblick

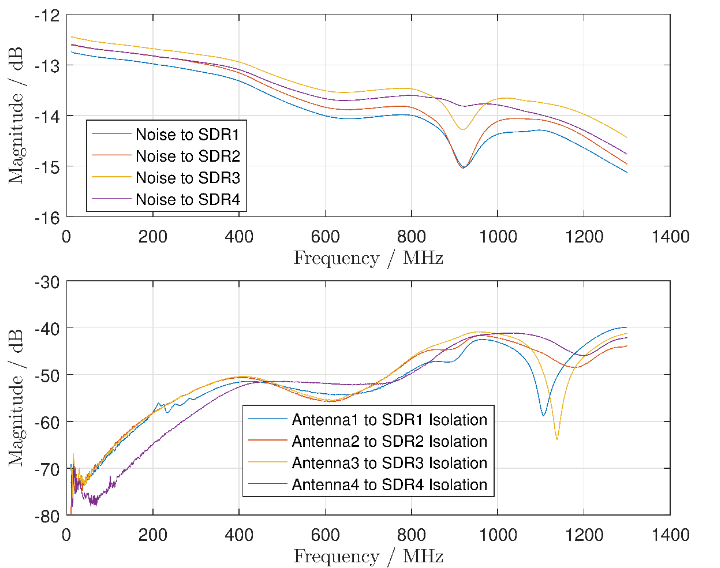

Überprüfung und Messung

▪ S- Parameter mit einem Zwei-Port-Vektor-Netzwerkanalysator

• Größe von S.21

➢ Überprüfung der PCB-Funktionalität

• Winkel von S.21

➢ PCB-Phasenkorrektur

Überprüfung und Messung

▪ HF-Schalter auf Rauschempfang eingestellt

Überprüfung und Messung

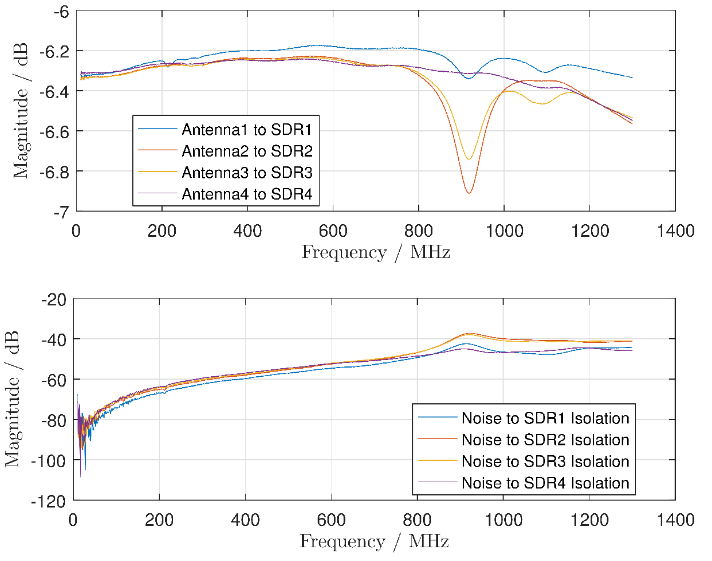

▪ HF-Schalter auf Antennensignalempfang eingestellt

Überprüfung und Messung

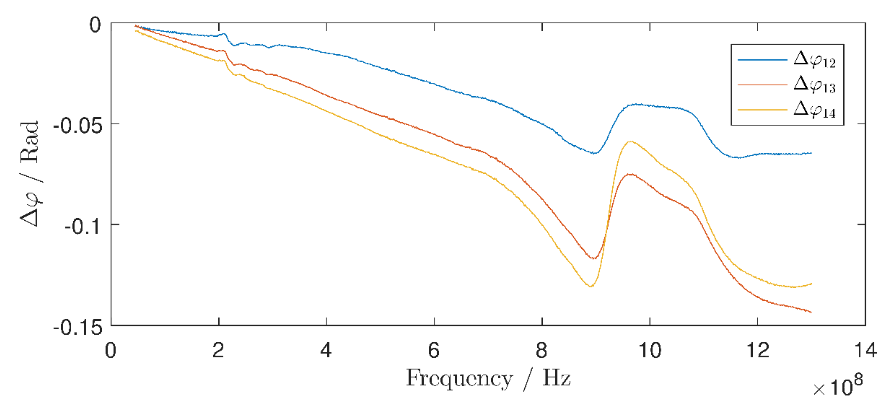

▪ Phasenversatz durch Leiterplatte hinzugefügt

Überprüfung und Messung

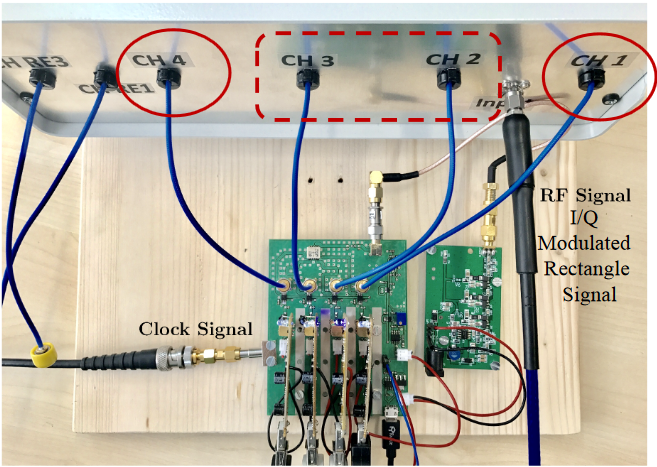

▪ Messeinrichtung

• PC

• 12V Stromversorgung

• Signalgenerator

• 28,8-MHz-Taktquelle

Ausgangssignal mit der gleichen Phase

Überprüfung und Messung

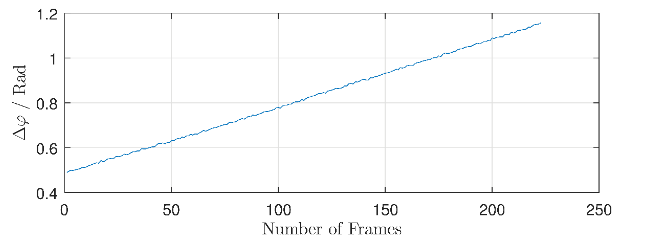

▪ Messergebnisse

• Ohne Phasendriftkompensation

• Mit Phasendriftkompensation

Überprüfung und Messung

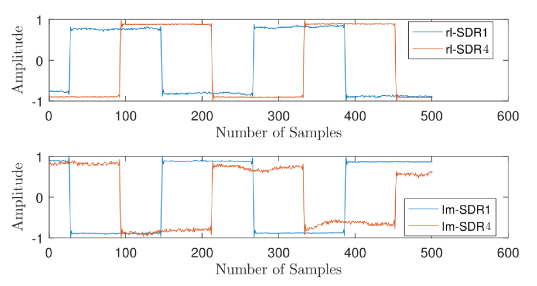

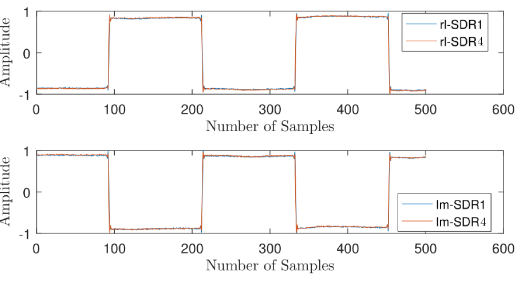

▪ Messergebnisse

Vor Zeit, Phase und Frequenz Synchronisation

Nach Zeit, Phase und Frequenz Synchronisation

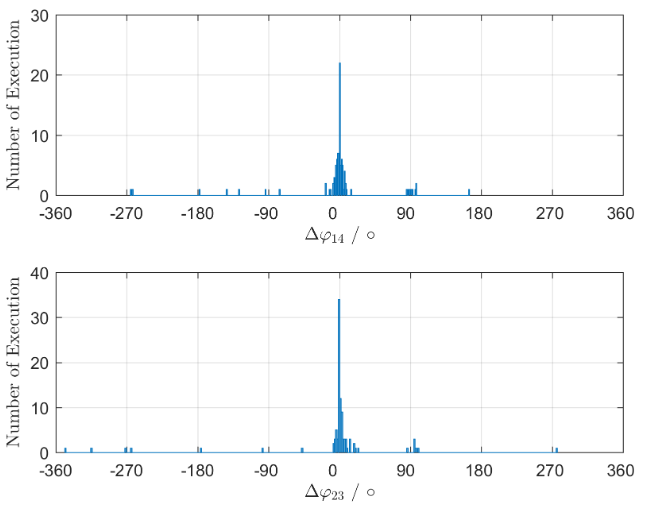

Überprüfung und Messung

▪ Messergebnisse

Fazit:

▪ Ein vierkanaliger kohärenter Empfänger basierend auf der Synchronisation von RTL-

SDRs wurden realisiert

▪ Der Restfrequenzfehler aufgrund der gebrochenen N- PLL war

erfolgreich von 250 auf 1350MHz kompensiert

▪ Die Synchronisation zeigt eine recht robuste Leistung bei 433 MHz, solange

die Phasendrift kontinuierlich ist

Weitere Arbeiten

▪ Kühlung und Abschirmung

▪ Messung bei höheren Frequenzen

▪ AGC für das Referenzrauschensignal

▪ Anwendungsdemonstration

▪ Timer

▪ HF-Schalter

▪ Taktverteilung

▪ Rauschquellen-Netzschalter

Hardware- und Software-Implementierung

HF-Schalter

▪ ADG918

• Saugfähiger SPDT-HF-Schalter

▪ SCA-4-132 +

• 4-Wege-Leistungsteiler

• Phasenunwucht muss kompensiert werden!

▪ Pad mit minimalem Verlust

• Bereitstellung einer Breitband-Impedanzanpassung von 50 Ω bis 75 Ω

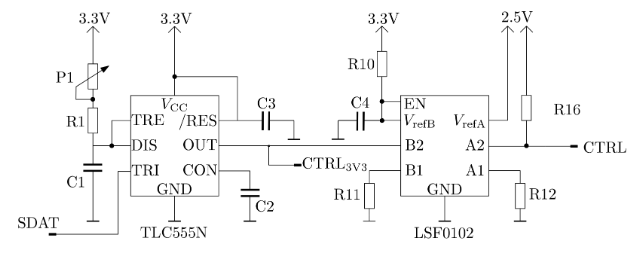

Hardware- und Software-Implementierung

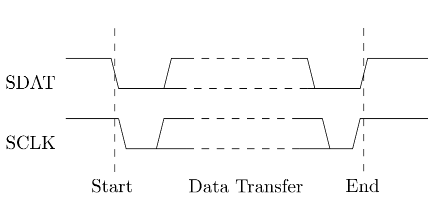

Triggersignal

▪ SDAT als Triggersignal

• I2C-Kommunikation zwischen Tuner-Chip R820T / EEPROM und

Demodulator-Chip RTL2832U tritt nur am Anfang der RTL-SDR-Konfiguration auf.

• Die I2C-Kommunikation beginnt mit einer fallenden Flanke bei SDAT während SCLK

hoch bleibt und endet mit einer steigenden Flanke bei SDAT, während SCLK

hoch bleibt.

Hardware- und Software-Implementierung

Timer

▪ TLC555

• Zeitschaltkreis für geringen Stromverbrauch

• Fallende Flanke ausgelöst

▪ LSF0102

• Spannungspegelübersetzer

• Öffnen Sie den Abfluss und drücken Sie Pull-kompatibel

Hardware- und Software-Implementierung

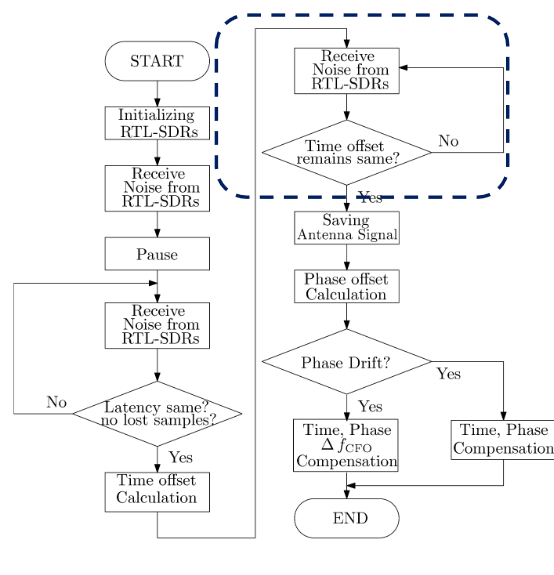

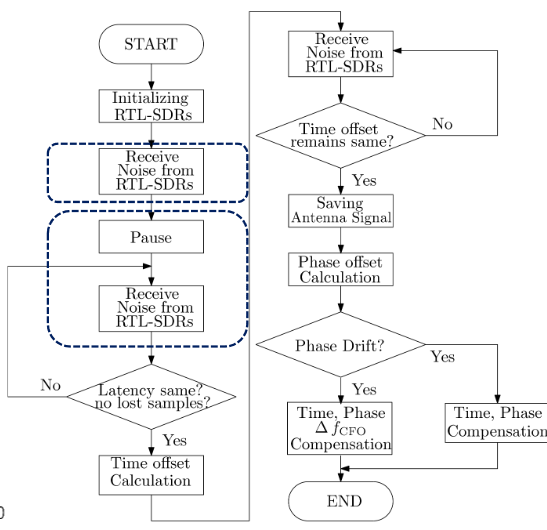

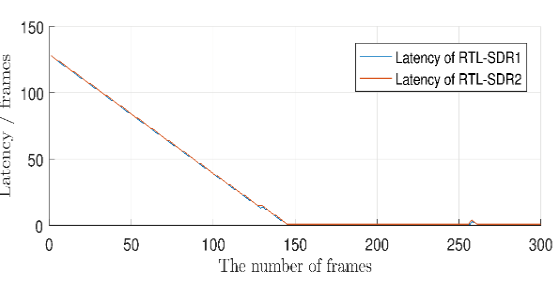

Synchronisationsalgorithmus

▪ Latenzzeitunterschied zwischen Kanälen

innerhalb der ersten Verarbeitungsschleife

▪ Die Latenz nimmt innerhalb einer Sekunde ab

Verarbeitungsschleife, bis keine Latenz mehr vorliegt.

Unterschied zwischen RTL-SDRs

Hardware- und Software-Implementierung

Synchronisationsalgorithmus

▪ Bestimmung wann das Antennensignal

bzw. wann der Empfang beginnt.